# **1Gb DDR2 SDRAM Specification**

#### Specifications

- Density: 1G bits

- Organization

- 8 banks x 16M words x 8 bits

- $\circ$  8 banks x 8M words x 16 bits

- Package

- o 60-ball FBGA (x8)

- 84-ball FBGA (x16)

- Lead-free(RoHS compliant)

- Power supply

- V<sub>DD</sub>,V<sub>DDQ</sub>=1.7 to 1.9V

- Data Rate: 1066Mbps/800Mbps

- 1KB page size (x8)

- Row address: AX0 to AX13

- Column address: AY0 to AY9

- 2KB page size (x16)

- Row address: AX0 to AX12

- Column address: AY0 to AY9

- Eight internal banks for concurrent operation

- Interface: SSTL\_18

- Burst lengths (BL): 4 , 8

- Burst type (BT):

- o Sequential

- o Interleave

- CAS latency (CL): 3, 4, 5, 6, 7

- Precharge: Auto precharge option for each burst access

- Driver strength: Normal/Weak

- Low self-refresh current (IDD6) parts are available

- Refresh: auto-refresh, self-refresh

- Refresh cycles: 8192 cycles/64ms

- Average auto-refresh period

- 7.8us at TC  $\leq$  +85°C

- 3.9us at TC > +85°C

- Automotive grade 3 compliant with AEC-Q100 grade 3

- Automotive grade 2 compliant with AEC-Q100 grade 2

- Operating case temperature range

- TC = 0°C to +85°C (Commercial grade)

- TC = -40°C to +95°C (Industrial range)

- $\circ$  TC = -40°C to +95°C (Automotive grade 3)

- TC = -40°C to +105°C (Automotive grade 2)

#### Features

- Double data-rate architecture: two data transfers per clock cycle

- The high-speed data transfer is realized by the 4 bits prefetch pipelined architecture

- Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver

- DQS is edge-aligned with data for READs; center- aligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- Data mask (DM) for write data

- Posted CAS by programmable additive latency for better command and data bus efficiency

- On-Die-Termination for better signal quality

- Programmable RDQS, /RDQS output for making x8 organization compatible with x4 organization

- /DQS, (/RDQS) can be disabled for single-ended Data Strobe operation

- Off-Chip Driver (OCD) impedance adjustment is not supported

# **Table of Contents**

| 1Gb D | DR2 SDRAM Specification    | . 1 |

|-------|----------------------------|-----|

| 1.    | Ordering Information       | . 3 |

| 2.    | Package Ball Assignment    | .4  |

| 3.    | Package outline drawing    | . 5 |

| 4.    | Electrical Specifications: | . 7 |

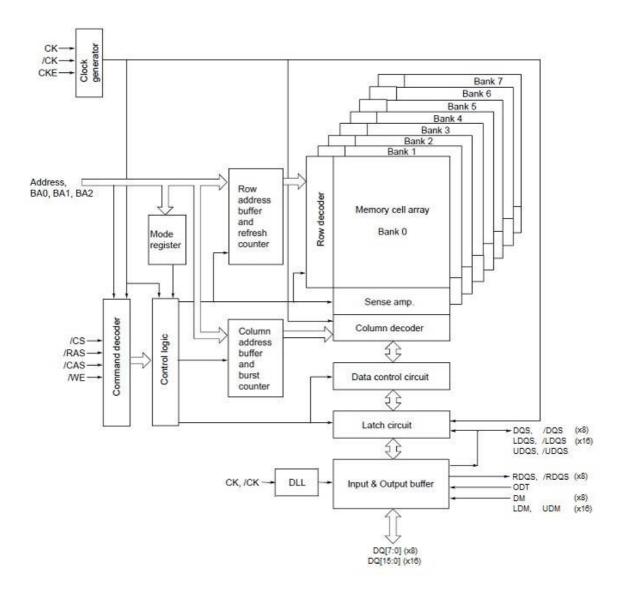

| 5.    | Block Diagram              | 15  |

| 6.    | Pin function               | 16  |

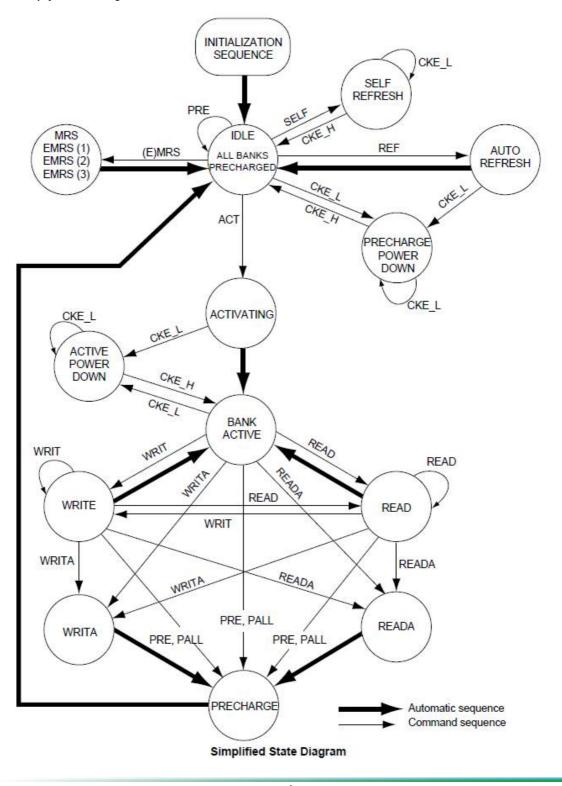

| 7.    | Command Operation          | 18  |

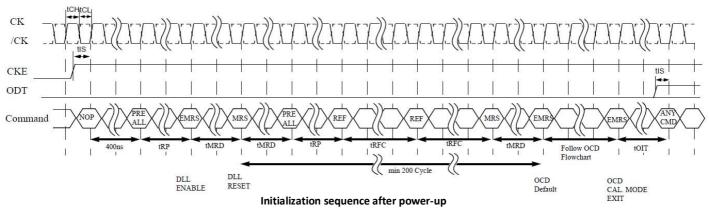

| 8.    | Functional Description     | 19  |

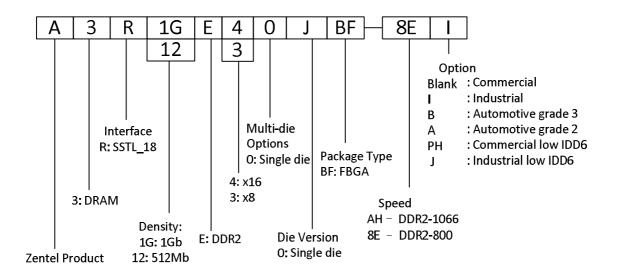

## 1. Ordering Information

| Part Number                   | Organization<br>(words x bits) | Internal<br>Banks | Speed bin<br>(CL-tRCD-tRP) | Package      | Note     |

|-------------------------------|--------------------------------|-------------------|----------------------------|--------------|----------|

| A3R1GE30JBF-8E/-8EI/-8EB/-8EA | 128M × 8                       | 0                 | DDR2-800 (5-5-5)           | 60-ball FBGA |          |

| A3R1GE30JBF-AH/-AHI/-AHB/-AHA | 128101 × 8                     | 8                 | DDR2-1066 (7-7-7)          | 60-Dali FBGA |          |

| A3R1GE40JBF-8E/-8EI/-8EB/-8EA | 64M × 16                       | 8                 | DDR2-800 (5-5-5)           | 84-ball FBGA |          |

| A3R1GE40JBF-AH/-AHI/-AHB/-AHA | 04101 × 10                     | õ                 | DDR2-1066 (7-7-7)          | 84-Dall FBGA |          |

| A3R1GE40JBF-8EPH              | 64M × 16                       | 8                 | DDR2-800 (5-5-5)           | 84-ball FBGA |          |

| A3R1GE40JBF-8EJ               | 64M × 16                       | 8                 | DDR2-800 (5-5-5)           | 84-ball FBGA | Low IDD6 |

| A3R1GE30JBF-8EJ               | 128M × 8                       | 8                 | DDR2-800 (5-5-5)           | 60-ball FBGA |          |

84-ball FBGA (×16 organization)

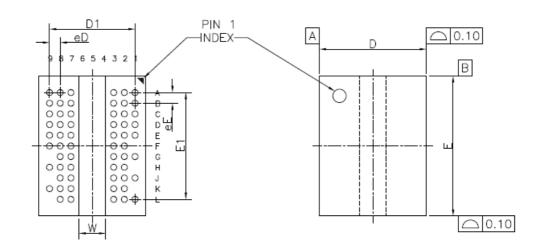

## 2. Package Ball Assignment

x8 : "60-Ball FBGA – 8x10.5mm, ball pitch 0.8mm, ball size 0.45mm. (package code BF)" x16 : "84-Ball FBGA – 8x12.5mm, ball pitch 0.8mm, ball size 0.45mm. (package code BF)"

| 60-ball FBGA<br>(×8 organization) |           |               |              |  |            |           |           |  |

|-----------------------------------|-----------|---------------|--------------|--|------------|-----------|-----------|--|

|                                   | 1         | 2             | 3            |  | 7          | 8         | 9         |  |

| A                                 |           | O<br>IU/ /RDG | O<br>Is Vss  |  | O<br>VSSQ  | O<br>/DQS |           |  |

| В                                 |           | O<br>VSSQ I   | O<br>DM/RDQS |  | DQS        | O<br>VSSQ | O<br>DQ7  |  |

| С                                 | O<br>VDDQ |               |              |  | O<br>VDDQ  | O<br>DQ0  | O<br>VDDQ |  |

| D                                 | O<br>DQ4  | VSSQ          | DQ3          |  | DQ2        | 0<br>VSSQ |           |  |

| Е                                 |           | O<br>VREF     | O<br>VSS     |  | O<br>VSSDL | ОСК       |           |  |

| F                                 |           | О<br>СКЕ      | O<br>/WE     |  | O<br>/RAS  | O<br>/CK  | ODT       |  |

| G                                 | O<br>BA2  | O<br>BA0      | O<br>BA1     |  | O<br>/CAS  | O<br>/cs  |           |  |

| Н                                 |           | 0<br>A10      | O<br>A1      |  | O<br>A2    | O<br>A0   |           |  |

| J                                 | O<br>VSS  | O<br>A3       | O<br>A5      |  | AG         | O<br>A4   |           |  |

| K                                 |           | O<br>A7       | O<br>A9      |  | 0<br>A11   | O<br>A8   | O<br>VSS  |  |

| L                                 |           | O<br>A12      | O<br>NC      |  | O<br>NC    | 0<br>A13  |           |  |

| (Top view)                        |           |               |              |  |            |           |           |  |

|    | 1                      | 2                    | 3                    | 7                      | 8         | 9         |

|----|------------------------|----------------------|----------------------|------------------------|-----------|-----------|

| A  |                        | O<br>NC              | O<br>VSS             | O<br>VSSQ              |           | O<br>VDDQ |

| в  | O<br>DQ14              | O<br>VSSQ            | O<br>UDM             | 0<br>UDQS              |           |           |

| С  | O<br>DQ14<br>O<br>VDDQ | O<br>DQ9             |                      | O<br>VDDQ              | O<br>DQ8  | O<br>VDDQ |

| D  |                        | VSSQ                 |                      |                        |           |           |

| E  |                        | ONC<br>NC            | O<br>VSS             | VSSQ                   |           | VDDQ      |

| F  |                        | O<br>VSSQ            |                      |                        | O<br>VSSQ | O<br>DQ7  |

| G  |                        |                      |                      | VDDQ                   | DQO       | O<br>VDDQ |

| Н  |                        | O<br>VSSQ            | O<br>DQ3             | DQ2                    | O<br>VSSQ |           |

| J  |                        |                      | O<br>VSS             |                        | Оск       | VDD       |

| K  |                        | O<br>CKE<br>O<br>BA0 | O<br>/WE<br>O<br>BA1 | O<br>/RAS              | О<br>/СК  |           |

| L  | O<br>BA2               | O<br>BA0             | O<br>BA1             | O<br>/RAS<br>O<br>/CAS | O<br>/CS  |           |

| M  |                        | A10                  | A1                   | 0                      | O AO      | VDD       |

| N  | O<br>VSS               | O<br>A3              | O<br>A5              | A2<br>0<br>A6          | O<br>A4   |           |

| Ρ  |                        | A7                   | O<br>A9              | O<br>A11               | O<br>A8   | O<br>VSS  |

| R  |                        | O<br>A12             | NC                   | O NC                   | NC        |           |

| 55 |                        |                      |                      |                        |           |           |

(Top view)

| Pin name        | Function                 | Pin name | Function                     |

|-----------------|--------------------------|----------|------------------------------|

| A0 to A13       | Address inputs           | ODT      | ODT control                  |

| BA0 to BA2      | Bank select              | VDD      | Power Supply                 |

| DQ0 to DQ15     | Data input/output        | VSS      | Ground                       |

| DQS, /DQS       |                          | VDDQ     | Power Supply for DQ circuit  |

| UDQS, /UDQS     | Differential data strobe | VSSQ     | Ground for DQ circuit        |

| LDQS, /LDQS     |                          | VREF     | Input reference voltage      |

| /CS             | Chip select              | VDDL     | Power Supply for DLL circuit |

| /RAS, /CAS, /WE | Command input            | VSSDL    | Ground for DLL circuit       |

| CKE             | Clock enable             | NC       | No connection                |

| СК, /СК         | Differential clock input | NU       | Not usable                   |

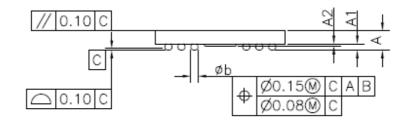

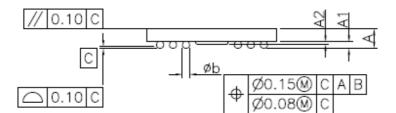

### 3. Package outline drawing

x8,60-ball FBGA

Solder ball: Lead free (Sn-Ag-Cu)

Unit: mm

| Cumphial | MILI     | MILLIMETERS |       |  |  |  |

|----------|----------|-------------|-------|--|--|--|

| Symbol   | MIN.     | NOM.        | MAX.  |  |  |  |

| Α        |          |             | 1.20  |  |  |  |

| A1       | 0.30     | 0.35        | 0.40  |  |  |  |

| A2       | 0.10     | 0.15        | 0.20  |  |  |  |

| D        | 7.90     | 8.00        | 8.10  |  |  |  |

| D1       | 6.       | 40 BS       | С     |  |  |  |

| E        | 10.40    | 10.50       | 10.60 |  |  |  |

| E1       | 8.       | 00 BS       | С     |  |  |  |

| b        | 0.40     | 0.45        | 0.50  |  |  |  |

| eD       | 0.80 BSC |             |       |  |  |  |

| еE       | 0.80 BSC |             |       |  |  |  |

| W        | 2.       | 00 BS       | С     |  |  |  |

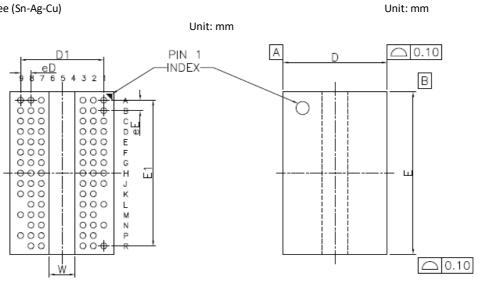

### x16 , 84-ball FBGA Solder ball: Lead free (Sn-Ag-Cu)

| Sumbol | MIL      | MILLIMETERS |       |  |  |  |

|--------|----------|-------------|-------|--|--|--|

| Symbol | MIN.     | NOM.        | MAX.  |  |  |  |

| A      |          |             | 1.20  |  |  |  |

| A1     | 0.30     | 0.35        | 0.40  |  |  |  |

| A2     | 0.10     | 0.15        | 0.20  |  |  |  |

| D      | 7.90     | 8.00        | 8.10  |  |  |  |

| D1     | 6.       | 40 BS       | С     |  |  |  |

| E      | 12.40    | 12.50       | 12.60 |  |  |  |

| E1     | 11       | 1.20 B      | SC    |  |  |  |

| b      | 0.40     | 0.45        | 0.50  |  |  |  |

| eD     | 0.80 BSC |             |       |  |  |  |

| еE     | 0.80 BSC |             |       |  |  |  |

| W      | 2.       | 00 BS       | С     |  |  |  |

### 4. Electrical Specifications:

All voltages are referenced to each GND level (VSS and VSSQ).

Execute power-up and Initialization sequence before proper device operation can be achieved.

#### 4.1 Absolute Maximum Ratings

| Parameter                       | Symbol | Rating       | Unit | Note |

|---------------------------------|--------|--------------|------|------|

| Power supply voltage            | VDD    | -1.0 to +2.3 | V    | 1    |

| Power supply voltage for output | VDDQ   | -0.5 to +2.3 | V    | 1    |

| Power supply voltage for DLL    | VDDL   | -0.5 to +2.3 | V    | 1    |

| Input voltage                   | VIN    | -0.5 to +2.3 | V    | 1    |

| Output voltage                  | VOUT   | -0.5 to +2.3 | V    | 1    |

| Storage temperature             | Tstg   | - 55 to +150 | °C   | 1, 2 |

| Power dissipation               | PD     | 1.0          | W    | 1    |

Notes:

1. Stresses greater than those listed under Absolute Maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Storage temperature is the case surface temperature on the center/top side of the DRAM.

#### Caution

Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### 4.2 Operating Temperature Condition

| Product grades     | Parameter                  | Symbol | Rating     | Unit | Note    |

|--------------------|----------------------------|--------|------------|------|---------|

| Commercial         |                            | тс     | 0 to +85   | °C   | 1, 2, 3 |

| Industrial         |                            | тс     | -40 to +95 | °C   | 1, 3    |

| Automotive grade 3 | Operating case temperature | тс     | -40 to +95 | °C   | 1, 3    |

| Automotive grade 2 |                            | тс     | -40 to 105 | °C   | 1, 3    |

Notes :

- 1. Operating temperature is the case surface temperature on the center/top side of the DRAM.

- 2. Supporting 0 to +85°C with full AC and DC specifications.

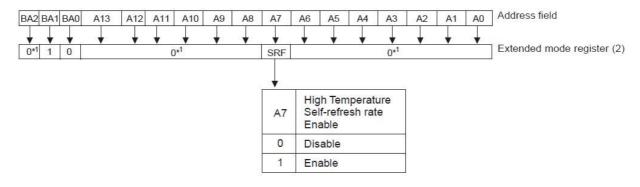

- Supporting up to +85°C and being able to extend to +95°C or +105°C (Automotive grade 2 only) with doubling autorefresh commands in frequency to a 32ms period (tREFI = 3.9μs) and higher temperature Self-Refresh entry via A7 "1" on EMRS(2).

#### 4.3 Recommended DC Operating Conditions(SSTL\_18)

| Parameter                       | Symbol   | min.         | typ.        | max.         | Unit | Note |

|---------------------------------|----------|--------------|-------------|--------------|------|------|

| Power Supply voltage            | VDD      | 1.7          | 1.8         | 1.9          | V    | 4    |

| Power Supply voltage for output | VDDQ     | 1.7          | 1.8         | 1.9          | V    | 4    |

| Power Supply voltage for DLL    | VDDL     | 1.7          | 1.8         | 1.9          | V    | 4    |

| Input reference voltage         | VREF     | 0.49 x VDDQ  | 0.50 x VDDQ | 0.51 x VDDQ  | V    | 1.2  |

| Termination voltage             | VTT      | VREF - 0.04  | VREF        | VREF + 0.04  | V    | 3    |

| DC input logic high             | VIH (DC) | VREF + 0.125 | -           | VDDQ + 0.3   | V    |      |

| DC input logic low              | VIL (DC) | -0.3         | -           | VREF - 0.125 | V    |      |

| AC input logic high             | VIH (AC) | VREF + 0.200 | -           | -            | V    |      |

| AC input logic low              | VIL (AC) | -            | -           | VREF - 0.200 | V    |      |

Notes:

- 1. The value of VREF may be selected by the user to provide optimum noise margin in the system. Typically the value of VREF is expected to be about 0.5 x VDDQ of the transmitting device and VREF are expected to track variations in VDDQ.

- 2. Peak to peak AC noise on VREF may not exceed ±2% VREF (DC)

- 3. VTT of transmitting device must track VREF of receiving device.

- 4. VDDQ tracks with VDD, VDDL tracks with VDD. AC parameters are measured with VDD, VDDQ and VDDL tied together.

4.4 Overshoot / Undershoot Specification

[Refer to section 6 in JEDEC Standard No. JESD79-2F and section 5 in JESD208]

#### 4.5 DC Characteristics

| Parameter                          | Test Condition                                                                                                                                  | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ļ   | 0   | Unit |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| ratameter                          |                                                                                                                                                 | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | X8  | X16 | onit |

| Operating current                  | one bank;<br>tCK = tCK (IDD), tRC = tRC (IDD), tRAS min. (IDD);<br>CKE is H, /CS is H between valid commands;                                   | IDD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -8E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70  | 70  | mA   |

| (ACT- PRE)                         | Address bus inputs are SWITCHING;<br>Data bus inputs are SWITCHING                                                                              | 8E708E70-AH75-AH75-AH75-AH80-AH80-AH20-AH20-AH30-AH30-AH30-AH30-AH30-AH30-AH30-AH30-AH401DD2N-AH-AH401DD3P-F-AH-AH401DD3P-F-AH-AH401DD3P-F-AH-AH40-AH50-AH70-AH70-AH70-AH135-AH135-AH145-AH165-AH165-AH165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75  | mA  |      |

| Operating current                  | one bank; IOUT = 0mA; BL = 4,CL = CL(IDD), AL = 0;<br>tCK = tCK (IDD), tRC = tRC (IDD);<br>tRAS =tRAS min. (IDD); tRCD = tRCD (IDD);            | IDD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -8E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75  | 75  | mA   |

| (ACT-READ-PRE)                     | CKE is H, /CS is H between valid commands;<br>Address bus inputs are SWITCHING;<br>Data pattern is same as IDD4W                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | X8      X16        -8E      70      70        -AH      75      75        -AH      75      75        -AH      80      80        -AH      25      25        -AH      35      35        -AH      35      35        -AH      40      40        -AH      40      40        -AH      45      45        -AH      40      40        -AH      75      75        -AH      75      75        -AH      75      75        -AH      75      75 | 80  | mA  |      |

| Precharge power-                   | all banks idle; tCK = tCK (IDD);CKE is L;<br>Other control and address bus inputs are STABLE;                                                   | IDD2P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -8E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20  | 20  | mA   |

| down standby current               | Data bus inputs are FLOATING                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -AH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25  | 25  | mA   |

| Precharge quiet                    | all banks idle; tCK = tCK (IDD);<br>CKE is H, /CS is H;                                                                                         | IDD2Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -8E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30  | 30  | mA   |

| Standby current                    | Other control and address bus inputs are STABLE;<br>Data bus inputs are FLOATING                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -AH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35  | 35  | mA   |

| Idle standby current               | all banks idel tCK = tCK (IDD);CKE is H, /CS is H;<br>Other control and address bus inputs are SWITCHING;                                       | ואניסטו                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -8E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35  | 35  | mA   |

|                                    | Data bus inputs are SWITDCHING                                                                                                                  | IDDZIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -AH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40  | 40  | mA   |

| Active power–down                  | All banks open; tCK = tCK (IDD); CKE is L;                                                                                                      | 10030 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -8E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40  | 40  | mA   |

| Standby current<br>(Fast PND Exit) | Other control and address bus inputs are STABLE;<br>Data bus input are Floating; MRS(12)=0                                                      | IDD3P-F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -AH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45  | 45  | mA   |

| Active power–down                  | All banks open;tCK = tCK (IDD); CKE is L;                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -8E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35  | 35  | mA   |

| Standby current<br>(Slow PND Exit) | Other control and address bus inputs are STABLE;<br>Data bus input are Floating; MRS(12)=1                                                      | IDD3P-S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -AH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40  | 40  | mA   |

| Active standby                     | all banks open;<br>tCK = tCK (IDD); tRAS = tRAS max. (IDD), tRP = tRP (IDD);<br>GKF is U. (CS is U. batwasa uslid commande)                     | $ \frac{1}{1000} + \frac{1}{100} + $ | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |      |